![]() Introduction to Thermal-aware Floorplans

Introduction to Thermal-aware Floorplans

Slideshow

Edit

1. Introduction to Thermal-aware Floorplans

2. Challenges in 3D IC Thermal Management

3. 3D Thermal Test Vehicle Design

4. Heat Flux and Temperature Measurement in TTV

5. Methodology Overview: RSM in TTV

6. Joint-gap Effect on Thermal Behavior

7. Examining Floorplan Influence

8. Response Surface Model Validation

9. Experimentation and Simulation Overview

10. Central Composite Design for RSM

11. Joint-gap Influence on Thermal Resistance

12. Floorplan Variations and Hotspot Analysis

13. Future Directions in 3D IC Thermal Optimization

Introduction

1. Introduction to Thermal-aware Floorplans

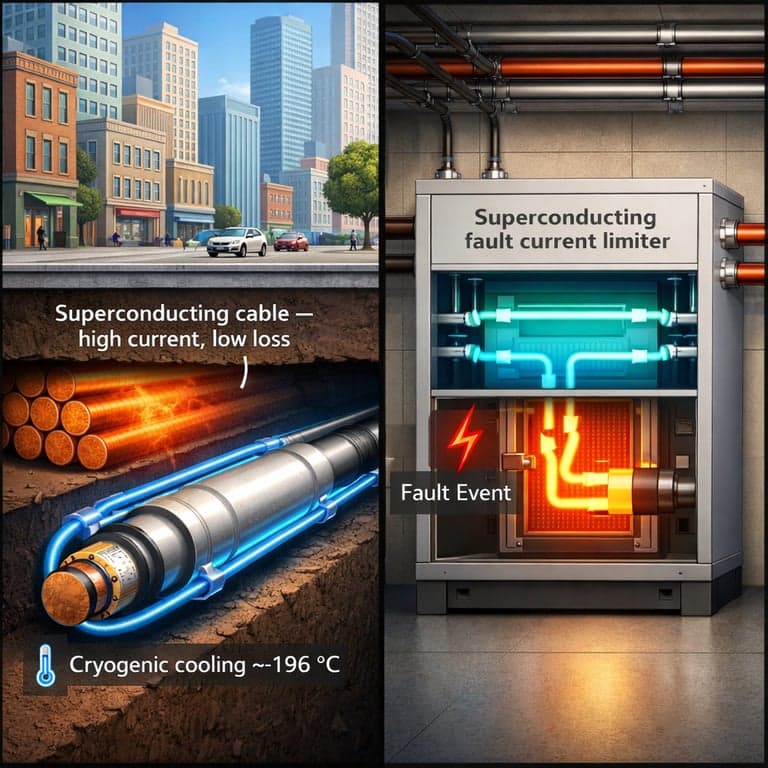

Exploring 3D IC's potential in reducing signal delay and power loss for high-computing systems.

2. Challenges in 3D IC Thermal Management

3D ICs face challenges like concentrated thermal stress and thermal coupling due to higher integration.

TTV Design and Methodology

3. 3D Thermal Test Vehicle Design

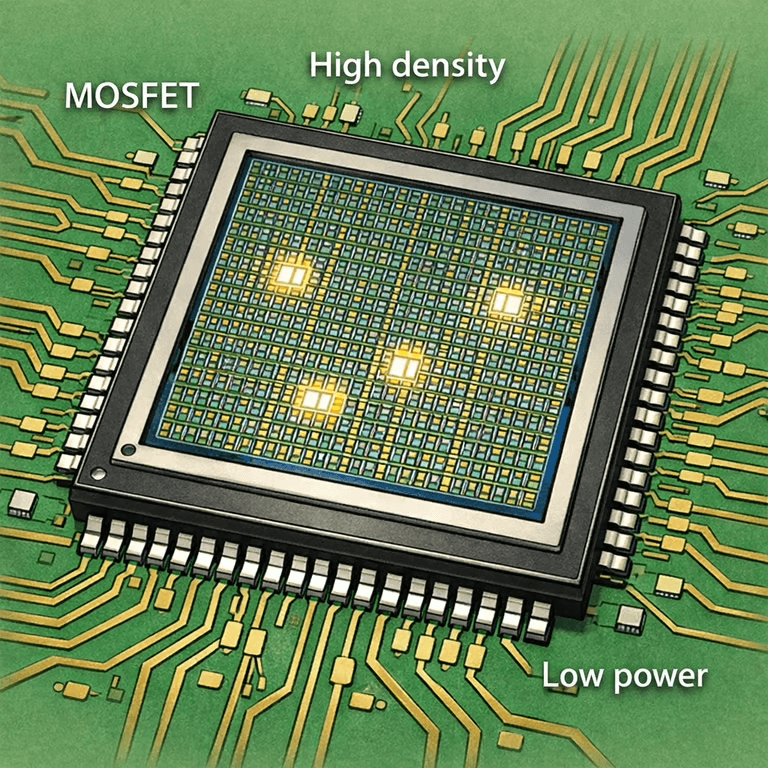

A 3D thermal test vehicle simulates real microprocessor using logic-SRAM or logic-logic dies with 18 heater blocks.

4. Heat Flux and Temperature Measurement in TTV

Each heater block dissipates up to 1.1 W/mm², with RTDs distributed across dies for local temperature monitoring.

5. Methodology Overview: RSM in TTV

Response Surface Methodology (RSM) estimates temperatures, showing close agreement with experimental data.

Analysis and Results

6. Joint-gap Effect on Thermal Behavior

Joint-gap acts as a thermal bottleneck, affecting thermal behavior and increasing junction-ambient thermal resistance.

7. Examining Floorplan Influence

Floorplan affects thermal coupling, altering junction temperatures and peak-to-peak temperature differences.

8. Response Surface Model Validation

Quadratic response models validated against experimental data, achieving over 95% reliability within ±5% error.

Experimentation

9. Experimentation and Simulation Overview

Experiment setup includes a fluidic circuit with minichannels, pump, heat exchangers, and a Coriolis flow meter.

10. Central Composite Design for RSM

Central Composite Design (CCD) used for RSM experiments with varied heat flux ranges to determine thermal responses.

Results Discussion

11. Joint-gap Influence on Thermal Resistance

Changing the vertical location of heat sources affects the thermal resistance significantly, up to 21%.

12. Floorplan Variations and Hotspot Analysis

Adjacent hotspots increase junction temperature and temperature difference due to enhanced thermal coupling.

Conclusion

13. Future Directions in 3D IC Thermal Optimization

Next steps involve optimizing floorplans in 3D ICs to minimize junction temperatures and improve thermal efficiency.